# illtar EMBEDDED SYSTEMS VOLUME 4 IN SEPTEMB

Small Form Factors supplement

#### Chris A. Ciufo

Intel still Inside

#### **Duncan Young**

8640D powers on

#### John Wemekamp

Network security

#### **Guest Column**

Military commanders must always feel secure with their communications systems...

DO YOU?

#### Our expertise

Aculab has become a center of excellence for many agencies delivering network centric communications solutions for deployment in tactical and infrastructure networks throughout the defense technology sector. Our advanced enabling technologies and responsive commitment to bespoke engineering development provide essential interoperability and highly effective, redundant, reliable and scalable components that enable our partners to deliver secure applications for joint land, sea and air operations.

#### Our difference

When you invest in a partnership with Aculab, you get more than the highest quality media processing technology that has been optimized for your sector. Whether it's for military applications, contact centers, conferencing or fax technologies, you get the reassurance of a stable and proactive partner, offering continued support and enabling you to adapt to change before it happens.

#### Our technology brings you

- Reduced operating costs

- Faster time to market

- Improved margins and ROI

#### For further information

www.aculab.com/military info@aculab.com +1 781 433 6000 +44 (0) 1908 273802

#### The total solution for embedded storage

#### SATADOM

Vertical Type 128MB~8GB Read: 24MB/s(max.) Write: 14MB/s(max.) Horizontal Type Capacities: 128MB~8GB Read: 24MB/s(max.) Write: 14MB/s(max.) SSD Series

2.5" SATA 6000 Capacities: 8GB~128GB Read: 60MB/s(max.) Write: 40MB/s(max.) -40°C~+85°C Wide Temp. Available

2.5" ATA 6000 Capacities: 8GB~128GB Read: 60MB/s(max.) Write: 40MB/s(max.)

# i-DIMM Series Wide Temp.

SDRAM/DDR 1/DDR 2/DDR 3

#### 4000 Series-EDC/iCF Available

Vertical type 40/44pin

Horizontal type 40/44pin

iCF 4000 up to 16GB

128MB~8GB Read: 40MB/s(max.) Write: 20MB/s(max.)

#### **USB EDC Series**

Capacities: 256MB~2GB Read: 17MB/s(max.) Write: 10MB/s(max.)

Capacities: 256MB~4GB Read: 33MB/s(max.) Write: 22MB/s(max.)

InnoDisk USA Corporation

# EMBEDDED SYSTEM

September 2008 Volume 4 Number 6

#### **COLUMNS**

#### **Industry Analysis**

Crunch all you want, we'll make 8 more CPUs

By Don Dingee

#### Mil Tech Insider

Optical fiber connectivity for rugged, 10 embedded systems

By John Wemekamp

#### **Crosshairs Editorial**

Intel inside ... everything on 46

the battlefield By Chris A. Ciufo

#### Field Intelligence

Freescale Semiconductor's 8640D 3 MIL/COTS

rekindles SBC power

By Duncan Young

#### Legacy Software Migration

5 MIL/COTS Migrate safely using source code analysis

By Gwyn Fisher, Klocwork

#### DEPARTMENTS

12 **Daily Briefing: News Snippets**

By Sharon Schnakenburg

42, 45 **Editor's Choice Products**

#### ON THE COVER:

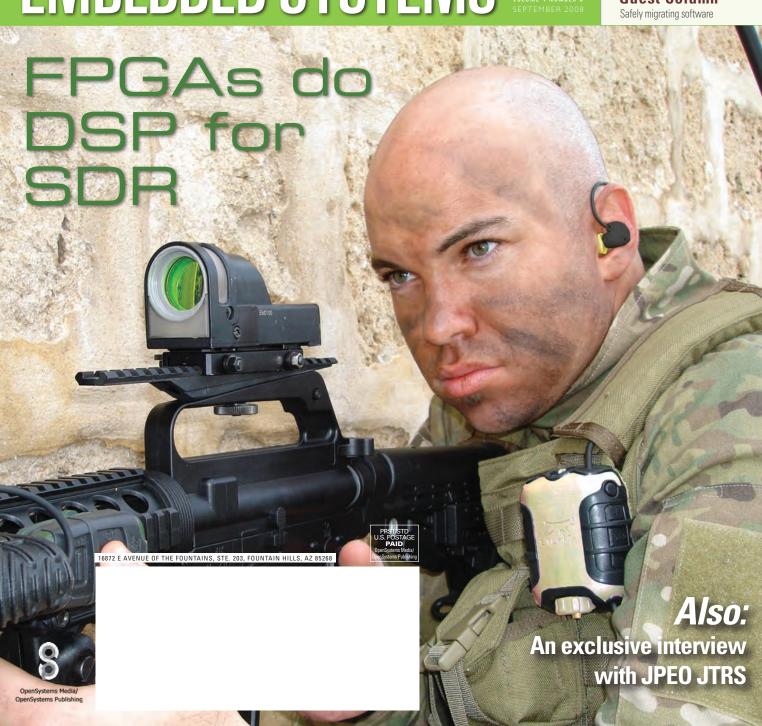

This Special Ops war fighter is wearing a software-defined tactical hearing enhancement headset, developed by Silynx Communications. Deployed by USSOCOM, the headset is but one example of how reconfigurable computing – usually enabled by FPGAs and DSP – is going beyond just Software-Defined Radios. But a software-defined, open architecture remains the backbone of the DoD's JTRS. Our exclusive interview with Dennis Bauman, JPEO JTRS, underscores that the program is back on track and already fielding working hardware. See articles starting on page 26. (Image courtesy of Silynx Communications.)

#### WEB RESOURCES

#### Subscribe to the magazine or E-letter:

www.opensystems-publishing.com/subscriptions

#### Live industry news:

www.mil-embedded.com/news www.opensystems-publishing.com/news/submit

#### Submit new products:

www.opensystems-publishing.com/np

Published by:

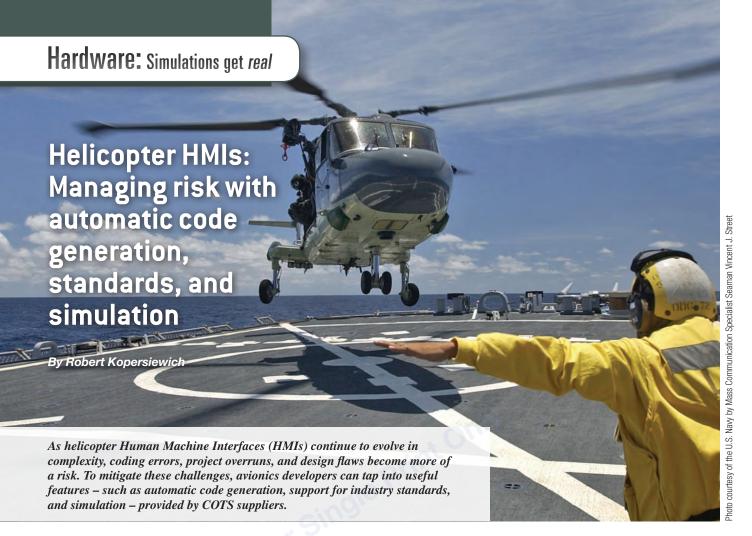

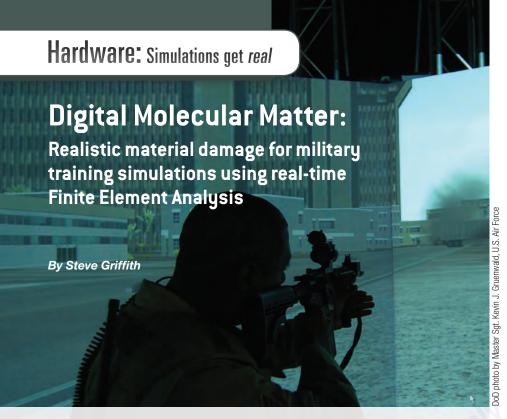

#### Hardware: Simulations get real

Helicopter HMIs: Managing risk with automatic code generation, standards, and simulation

By Robert Kopersiewich, Presagis

20 **Digital Molecular Matter:** Realistic material damage for military training simulations using real-time

**Finite Element Analysis**

By Steve Griffith, Objective Interface Systems

#### Technology: FPGAs do DSP for SDR

Back on track:

JTRS JPEO assures open SCA and coalition use

Q&A with Dennis M. Bauman, JTRS JPEO

30 Digital-Down Converter implementation, FPGAs offer new possibilities

By Bob Sgandurra and Rich Kuenzler, Pentek, Inc.

FPGAs for mission-critical applications

By Rajiv Jain and Mehul Kochar, QuickLogic

#### E-CASTS

www.opensystems-publishing.com/ecast

Low-power processors in SFFs

Oct. 8, 2008 • 2 p.m. EDT

Presented by: Freescale Semiconductor, Kontron, and EuroTech

Adapting the Eclipse IDE for embedded development

Oct. 21, 2008 • 2 p.m. EDT Presented by: Express Logic

#### **EVENTS**

Vision 2008 Embedded Linux Developers Conference

Oct. 1-3, 2008 • San Francisco, CA

www.mvista.com/vision

SDR '08 Technical Conference & Product Exposition

Oct. 26-29, 2008 • Washington, D.C. www.sdrforum.org/SDR08

#### Embedded Systems Conference – Boston

Oct. 26-30, 2008 • Boston, MA www.cmp-egevents.com/web/escb

#### **MILCOM 2008**

Nov. 17-19, 2008 • San Diego, CA www.milcom.org

All registered brands and trademarks within Military Embedded Systems magazine are the property of their respective owners.

© 2008 OpenSystems Media/OpenSystems Publishing © 2008 Military Embedded Systems

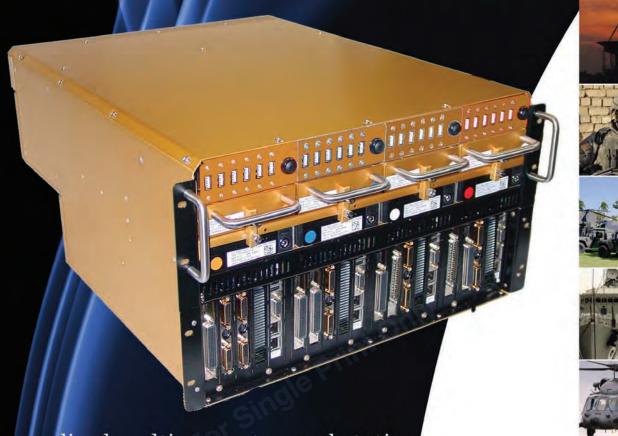

# The MISSION WORKSTATION

A ruggedized multi-computer workstation for applications that demand the best.

- 4 completely independent computer systems in one 19" 6U rack mount enclosure

Every Mission Workstation is screened to a ruggedized

- Every Mission Workstation is screened to a ruggedized production acceptance test including fully powered 3G NAVMAT vibration test and environmental stress screening (ESS) test.

- Can be factory configured to be powered from DC or AC sources

- All hard drives are removable

- Temperature range of -10C to 60C

- Each of the 4 computers can be independently configured with Core 2 Dual or Core 2 Quad Intel processors

- Supports multiple operating system configurations

- Can be factory configured as 4 independent computer systems or one cluster computer

- Each individual computer has 2 PCI slots, 1 PCIx-16 slot, up to 8G RAM, 4 SATA ports, 2 Gigabit Ethernet ports, and up to 12 USB 2.0 ports

- Jacyl Technology is the OEM of the Mission Workstation, contact us for custom configurations

Jacyl Technology specializes in the design and production of custom and COTS electronic systems for severe environment applications.

# ITATV EMBEDDED SYSTEMS

OPENSYSTEMS PUBLICATION

#### Military and Aerospace Group

- DSP-FPGA.com/E-letter

- DSP-FPGA.com Resource Guide

- Military Embedded Systems/E-letter

- Military Embedded Systems Resource Guide

- PC/104 and Small Form Factors/E-letter

- PC/104 and Small Form Factors Resource Guide

- VME and Critical Systems/E-letter

Group Editorial Director Chris A. Ciufo

cciufo@opensystems-publishing.com

Senior Editor (columns) Terri Thorson

tthorson@opensystems-publishing.com

**Associate Editor** Sharon Schnakenburg

sschnakenburg@opensystems-publishing.com

Assistant Editor Robin DiPerna New Products Editor Cliff Witte **European Representative** Hermann Strass

hstrass@opensystems-publishing.com

Senior Web Developer Konrad Witte Web Content Specialist Matt Avella **Creative Director** Steph Sweet **Art Director David Diomede** Circulation/Office Manager Phyllis Thompson

subscriptions@opensystems-publishing.com

#### OpenSystems Media/OpenSystems Publishing

Editorial/Production office:

16872 E. Ave of the Fountains, Ste 203, Fountain Hills, AZ 85268

Tel: 480-967-5581 Fax: 480-837-6466 Website: www.opensystems-publishing.com

Publishers John Black, Michael Hopper, Wayne Kristoff

Vice President Editorial Rosemary Kristoff

#### Communications Group

Editorial Director Joe Pavlat **Managing Editor** Anne Fisher **Technology Editor Curt Schwaderer European Representative** Hermann Strass Senior Designer Joann Toth

#### **Embedded and Test & Analysis Group**

**Editorial Director** Jerry Gipper **Editorial Director** Don Dingee Senior Associate Editor Jennifer Hesse Special Projects Editor **Bob Stasonis European Representative** Hermann Strass

Military Embedded Systems (USPS 019-288) is published eight times a year (January/February, March/April, May, June, July/August, September, October, November/December) by OpenSystems Media/OpenSystems Publishing LLC, 30233 Jefferson Avenue, St. Clair Shores, MI 48082. Subscriptions are free to persons interested in the design or promotion of Military Embedded Systems. For others inside the US and Canada, subscriptions are \$28/year. For 1st class delivery outside the US and Canada, subscriptions are \$50/year (advance payment in US funds required). Canada: Publication agreement number 40048627. Return address WDS, Station A PO Box 54,

POSTMASTER: Send address changes to *Military Embedded Systems* 16872 E. Ave of the Fountains, Ste 203, Fountain Hills, AZ 85268

DSP-FPGA.com

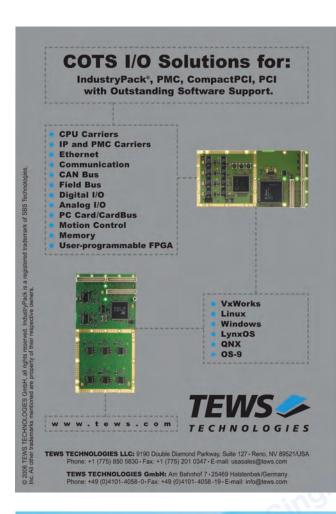

# Annapolis Micro Systems The FPGA Systems Performance Leader

# WILDSTAR 5 for IBM Blade The Perfect Blend of Processors and FPGAs

Fully Integrated into IBM Blade Management System

Abundant Power and Cooling Ensure Maximum Performance

Made in the USA

#### **Ultimate Modularity**

From 2 to 8 Virtex 5 FPGA/Memory Modules Input / Output Modules Include: Quad 130 MSps thru Quad 500 MSps A/D 1.5 GSps thru 2.2 GSps, Quad 600 MSps A/D Dual 1.5 GSps thru 4.0 GSps D/A Infiniband, 10 G Ethernet, FC4, SFPDP

Between EPGAs and Processors over IB or 10GE Backplane

Between FPGAs and Processors over IB or 10GE Backplane

Between FPGAs and Standard Output Modules

190 Admiral Cochrane Drive, Suite 130, Annapolis, Maryland USA 21401 wfinfo@annapmicro.com (410) 841-2514 www.annapmicro.com

#### **Industry Analysis**

# Crunch all you want, we'll make more CPUs

By Don Dingee

If the Apple purchase and integration of P.A. Semi goes as expected, the PWRficient has joined a long list of dead CPU technology inside a defense program somewhere near you: CDP1802, MIL-STD-1750A, Z8000, Am29000, and i80960. And Freescale is dead set on the dual-core 8641D being the last of the highend e600 Power Architecture designs, with its focus instead on designs like the QorIQ P4080 using eight smaller e500mc cores.

These are just more signs that the shift to consumer electronics has transformed the landscape for defense computing permanently. Getting any high-end CPU in a version with a higher junction temperature is difficult, and forget about getting a state-of-the-art CPU in a rad hard version. Building parts to meet defense requirements just isn't a money-making proposition for most companies.

When I wrote about this last year, I pointed out the solution might be, in part, boutique processors such as the Raytheon MONARCH. But at least one of the supporters of that architecture – Mercury Computer Systems – ended up not going that direction for production designs. "We can only support so many processor architectures," said my source. (The MONARCH uses an R3000-like instruction set, where most Mercury efforts center on Power Architecture devices.)

However, I don't think that means the concept of a reconfigurable processor in defense circles is dead. In fact, it appears that the opposite might be true – the idea might be very alive, out of necessity.

In 1990, while I was working on an IRAD project at a major defense contractor, the engineers across the hall were working on another interesting job. They were emulating the CDP1802 instruction set

with Altera MAX FPGAs, a fairly straightforward job for a simple architecture using only single-issue, in-order execution.

Processors have gotten much more complex, but with FPGA cores readily available for many processor architectures, "building" your own processor device is now feasible without all the work of emulating instruction sets. These devices won't have high-end CPU cores, but they will have enough horsepower to get the job done for most applications – and much more horsepower than things like the 1750A.

Using FPGAs delivers more benefits. With the other functionality in the FPGA, other features can be directly integrated with the processor core to innovate, save space, and improve performance. FPGAs are available in extended temperature ranges, with extended life cycles, and there are some rad hard FPGA lines available.

Two examples of companies on this not-so-beaten path include:

- CPU Tech (www.cputech.com, Pleasanton, CA) has introduced their Acalis CPU872 SoC, which they call a *field programmable multicore device*. Fabbed at IBM's Trusted Foundry, the part includes Power Architecture 440 cores, embedded DRAM, and several utility compute engines. The device also has anti-tampering and anti-reverse engineering features (really their focus), and is offered in an industrial temp range with a 10-year lifespan to select customers.

- Achronix Semiconductor (www.achronix.com, San Jose, CA) is working with BAE Systems on a rad hard FPGA using its high-performance FPGA technology. Achronix claims to have one line of current non-rad hard parts operating at near 2 GHz, and another line running near 1 GHz with a super wide -260 °C to +130 °C temperature range.

Ray Alderman of VITA is even on this bandwagon, calling on the audience at the 2008 Critical Embedded Systems MediaFest to "innovate outside traditional semiconductor offerings" using FPGAs in order to protect designs from CPU and other component obsolescence. Not the greatest marketing term for an initiative, but the idea is solid.

We might never see a return to the days when high-end processor vendors targeted defense markets, but as long as the FPGA players and CPU core IP providers stay in the game, there should be options. And we might see some very creative solutions rise from the ranks.

For more information, contact Don at ddingee@opensystems-publishing.com.

# MIL-STD-1553/ARINC 429

#### WHEN RELIABILITY COUNTS...

Four decades of time-proven *reliability*, thousands of design-ins, and long life cycle support, make DDC the one MIL-STD-1553 and ARINC 429 company you can rely on for generations to come.

#### Mil Tech Insider

#### Optical fiber connectivity for rugged, embedded systems

By John Wemekamp

Optical fiber is the transmission medium of choice for many military and aerospace applications because of its immunity to EMI, its lack of detectable electromagnetic emissions, its lower weight than copper cabling, and its ability to transmit high-speed signals over greater distances than equivalent copper connections. This makes it ideal for use as a secure, reliable intra-platform bus (Ethernet or Fibre Channel) or for the long-distance transmission of ultra-secure data. It has been widely adopted in commercial applications and also in less rugged military systems such as Naval combat systems and many fixed C4I installations such as battle command and air defense systems. However, the more widespread adoption of optical fiber within rugged, embedded applications has been inhibited by its incompatibility with some established embedded computing equipment, such as VMEbus and CompactPCI, resulting in suboptimal connectivity solutions.

The most rugged embedded computing applications are to be found in avionics (combat aircraft, helicopters, and missiles) and ground vehicles (tracked and wheeled armored vehicles). These two application spaces have similar requirements for packaging wherein space, weight, and power are at a premium plus conduction cooling is required to withstand the harsh environment. The military avionics market has seen the widespread adoption of the ARINC 404A ATR chassis standard, providing an ideal package size for 3U and 6U VME, CompactPCI, and VPX-based products. Maintenance procedures encourage backplane-only interconnection of modules within a chassis to prevent damage to loose cables and to prevent signals from incorrect rerouting after maintenance. Newer platforms are being designed for 2 level maintenance with Line Replaceable Modules (LRMs), which, while not constrained by ATR's limited dimensions, still cannot tolerate loose cables being plugged into the front panels.

Many interconnect solutions exist for optical fiber connection through a module's front panel. These are in widespread use in telecommunications and commercial applications. There are also many military specification (MIL-C-38999 type) optical panel connectors that can be fitted to the front of ATR boxes. However, none of these were designed for backplane connectivity in such a limited envelope space. An effective optical backplane connector must engage and disengage without the use of special tools or locking/unlocking devices, must provide very accurate alignment of fibers, and must work reliably in high-vibration military environments. Finally, in the confined space of an ATR box, the fibers must be routed from the rear of the backplane to their point of external connection without exceeding their minimum bend radius so as to not compromise signal or physical integrity of the fiber.

In order to resolve these issues and to provide a set of backplane standards for use with VPX, industry leaders, including Curtiss-Wright Controls Embedded Computing (CWCEC), are proposing a new standard, designated VITA 46.12. The standard is based on off-the-shelf fiber connector types that could be integrated with existing VPX backplane and module specifications. Three connector types, each with multiple independent vendors, are being evaluated:

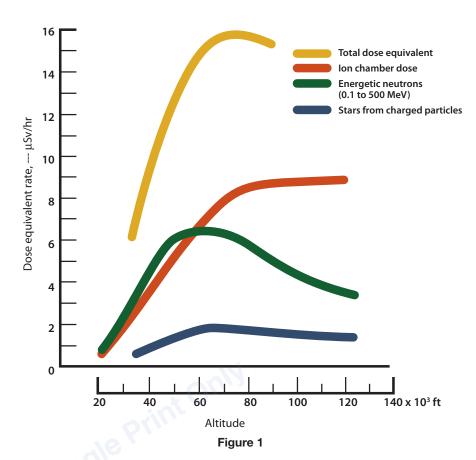

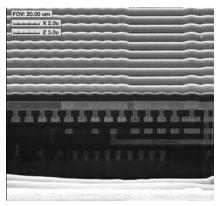

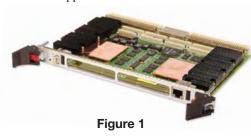

■ *Mechanical Transfer (MT)* – The MT type uses a self-aligning pair of mating shells and pins to maintain positional accuracy of fibers in the form of a ribbon cable. MT is an established commercial standard offering high connection density, but it needs care to maintain cleanliness and does not provide specific alignment of individual fibers. Figure 1 illustrates the concept of using an MT connector between a VPX module and backplane.

Figure 1

- Expanded Beam (EB) This uses a spherical lens at the end of each fiber to expand the beam to many times its size. Connection is made by bringing the two lenses into close proximity without physical contact. EB connectors are less sensitive to alignment or contamination and can tolerate many mating cycles without degradation.

- LuxCis-type of connectors designed for ARINC 801 aerospace applications These consist of metal shell pairs containing multiple signal connections using ceramic ferrules for fiber alignment, maintaining positional accuracy in high-vibration environments.

Fiber connectivity through the backplane has been an omission from embedded computing standards for too long. VITA 46.12 is supported by a broadly based industry working group of board vendors, end users, and connector vendors. It aims to develop a set of optimal connector choices based on established types supported by the results of further environmental testing. The VPX (VITA 46) standard is already proving a worthy successor to VMEbus, demonstrating its leadership by providing the first rugged, embedded computing standard for the practical use of fiber through the backplane.

To learn more, e-mail John at john.wemekamp@curtisswright.com.

# Simply Powerful. Powerfully Simple.

## High-performance FPGA I/O designed for faster and easier development.

Only Acromag gives you a reconfigurable FPGA wrapped with just the features you need for fast and easy implementation. These PMC modules provide a high-speed I/O interface with plenty of memory for efficient data handling.

- Virtex-5 FPGAs (VLX155T/110T/85T or VSX95T) are optimized for logic or DSP

- Two banks of high speed 32M x 16-bit DDR2 SDRAM handle high volumes of data

- Two banks of 256K x 32-bit dual-port SRAM optimize DMA transfer to the bus

- PCI-X 133MHz 64-bit interface ensures fast data throughput

- Engineering Design Kit speeds development of custom FPGA applications.

## Plug-in I/O cards extend the I/O capabilities

AXM I/O extension modules expand interface support for a wide variety of analog and digital I/O signals.

## Affordable FPGA-based I/O for all your projects

Acromag's full line of industry pack and PMC modules feature Xilinx FPGAs at a range of price and performance points. Why settle for generic I/O when you can costeffectively design just what you need? For details on the fastest and easiest way to develop FPGA I/O visit

AcromagEmbedded.com,

or call 1-877-295-7088

acromagembedded.com

solutions@acromag.com

877-295-7088 or 248-295-0310

## Daily Briefing: News Snippets

By Sharon Schnakenburg, Associate Editor

www.mil-embedded.com/dailybriefing

#### Semiconductor sales: Against the economic trend?

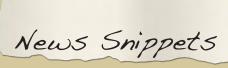

While the U.S. dollar continues to struggle, the worldwide semiconductor market isn't facing the same challenges, according to a recently released Semiconductor Industry Association (SIA) report. Findings indicate that worldwide semiconductor sales were at \$21.8 billion in May 2008, a 7.5 percent rise from the \$20.3 billion of May 2007. Meanwhile, May 2008 sales showed a 2.8 percent increase over the \$21.2 billion of April 2008. "Despite reports of declining consumer confidence in the U.S., both disposable income and consumer spending rose in May. It is likely that the distribution of tax rebate checks to millions of Americans was a factor in increased consumer spending," says George Scalise, SIA president. The report also states that "until recently" about 31 percent of sales of PC units were U.S. based, but that today's emerging consumer markets leave the U.S. accounting for only 21 percent at present. Additionally, SIA predicts that in 2008, the U.S. will account for only 13 percent of cell phone unit sales, compared to 21 percent five years ago.

#### Mission computer finds refuge

... or helps those on the battlefield seeking shelter, anyway. Accordingly, Smiths Detection, provider of Chemical Biological Protective Shelters (CBPSs), recently granted a through-2016 IDIQ contract to Parvus to provide its DuraCOR 810 mission computers for Smiths' highly mobile, contamination-free shelters. The shelters are built to protect combat service support personnel and medical combat services, and the COTS DuraCOR 810 will serve as processor subsystem therein. The rugged COTS DuraCOR 810 is deployed in several manned and unmanned aircraft, naval installations, and ground vehicles. It also meets the harsh environment requirements of MIL-STD-810F and the voltage/power surge requirements of MIL-STD-1275D and -704E.

#### **Bradley Combat System gets** new SoC

Production kits for the battle-ready and -proven Bradley Combat System will soon feature the Acalis Multicore System-on-Chip (SoC). Chosen by BAE Ground Systems, CPU Technology, Inc.'s Acalis CPU420 field-programmable SoCs are low-power, highly integrated units configurable to system requirements. The SoCs contain several processors, controllers, interfaces, memories, and critical functions while reducing board count. Acalis CPU420 is scheduled for a 19-month delivery span.

#### **New avionics safety groups** take flight

Commercial airplanes and select military aircraft aren't the only ones flying in DO-178B (software) and DO-254 (hardware) avionics safety-standard style. Now two new industry groups, the DO-254 Industry Group and the DO-178 Industry Group, are ascending into the world of engineering – and looking for members. The groups are designed to provide a central repository and serve as a router to fill avionics sector needs and "energize and synergize avionics development." The groups unite vendors, developers, service companies, and tool providers in providing products, white papers, and training. Both nonprofit groups also have their own blogs at www.do178blog.com and www.do254blog.com. For more information, visit www.do178site.com or www.do254site.com.

#### U.S. Navy selects GeneSiC – again

Perhaps the U.S. Navy can't get enough of a good thing – or at least not enough of the Silicon Carbide (SiC) devices offered by GeneSiC Semiconductor Inc. Consequently, the U.S. Navy's Naval Surface Warfare Center, which chose GeneSiC for its Phase I SBIR project, has now chosen the vendor for Phase II SBIR. The project centers on multi-kV SiC device development for both power distribution systems and power conditioning within modern and legacy ship bus infrastructures. And there's more ... the Navy's Space and Naval Warfare Systems Command (SPAWAR) also granted GeneSiC its Phase I SBIR award, which focuses on novel SiC device fabrication and design for high-power, high-frequency radar applications.

#### PikeOS is a 'GO for the DIANA project

SYSGO was recently chosen to supply its PikeOS virtualization RTOS platform for the European DIANA (Distributed, equipment Independent environment for Advanced AvioNics Applications) project. Led by Skysoft and funded by the European Commission's 6th Framework Programme, the DIANA project's goal is defining an "advanced" AIDA (Architecture for Independent Distributed Avionics) platform to support object-oriented applications' execution over secure distribution services and virtual machines. PikeOS, an ARINC-653 and MILS-compliant RTOS, will support AIDA's Flight Management System (FMS) test application.

#### **U.S. Army sends signals**

The U.S. Army recently enlisted Rohde & Schwarz's R&S SMB100M signal generators for duty. The contract between the two entities was initiated by the U.S. Army Aviation & Missile Command at Redstone Arsenal, AL. The agreement stipulates that Rohde & Schwarz provide 4,000 of its high-performance RF signal generators, along with optional support and service for seven years. The signal generators will be used for the Army's Test Equipment Modernization (TEMOD) program, which facilitates the replacement of obsolete general-purpose test equipment with off-the-shelf, state-of-the-art products. TEMOD's goal is to improve Army weapon systems readiness, reduce field equipment amounts, and cut costs of operations and support. The R&S SMB100M is a spin-off of the commercially available analog signal generator R&S SMB100A, which features a measurement range from 9 KHz to 6 GHz.

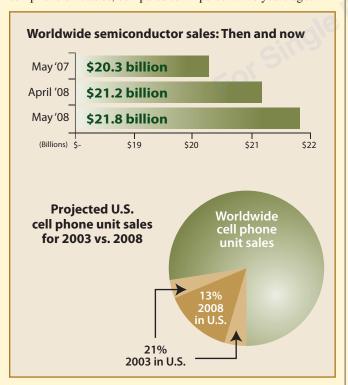

#### Do you see what I see?

Quantum3D Inc. recently got into the picture after QuantaDyn selected Q3D's Independence IDX 4000 Image Generator (IG) to provide upgrades to the U.S. Air Force's KC-135 Boom Operator Weapons System Trainer (BOWST). The BOWST training system helps prepare boom operators for service on the KC-135 Stratotanker, which provides in-flight refueling for Navy, Marine, Air Force, and allied nations' aircraft. Independence IDX 4000 will provide reflections on a 3D ocean, dynamic shadows, advanced weather effects, real-time lighting, alias elimination, and 8,192-pixel by 8,192-pixel shadow masks for BOWST as a result of Randolph Air Force Base's original request for upgrades. The upgraded BOWST's next stop is Altus Air Force Base.

Helicopter Human Machine Interfaces (HMIs) have changed dramatically since the first turbine helicopters, the Ka-225 and a modified Navy HTK-1, were introduced more than 50 years ago. What was initially comprised of mechanical fuel gauges and altimeters has been replaced with an integrated flight data system of computers and multifunction displays that provides the pilot with key navigational, weather, and other crucial flight information (Figure 1). Today, helicopter avionics continue to evolve at a rapid pace, increasing the complexity of their development.

Integrating next-generation displays and new information sources into pilotfriendly HMIs is not the only challenge faced by avionics developers today. Developers must also manage the project and consider development costs. When the turbine helicopter was introduced, only 5 percent of its cost was for avionics. Today, avionics account for approximately 60 percent of the aircraft costs.

Now that HMI development is more complex and costly, there is a greater risk of coding errors, project overruns, and design flaws. But with a little advanced

planning and the right tools, helicopter developers can stay ahead of the curve and provide customers with the most user-friendly, sophisticated HMI possible without incurring huge development costs and risks. Advances in COTS software are providing avionics developers the opportunity to take advantage of software tools that automate processes, support industry standards, and provide a platform for effectively testing the design before it is deployed in the cockpit.

#### Reduce risks with automatic code generation

To save time and reduce the risk of project overruns, designers should pay close attention to how they approach lowlevel requirements, which indicate how to write the software at the coding level without any further instruction necessary. Examples of low-level testing include the coding of objects and logic. While these features can be manually developed, hand coding requires manual bug fixing and

Figure 1

optimization, which can consume a lot of time at the project's outset. By using software with automatic code generation, low-level requirements are captured in the software's model and low-level testing is virtually eliminated. While high-level testing is still required, it is generally reduced because the code has been automatically generated and required little or no low-level testing. As the displays are created using a modeling tool, requirements are captured in early prototypes and reviews are completed early on. This can further reduce the need for high-level testing.

As the HMI moves from prototyping into production, developers must take extra care to reduce coding errors. Hand coding by nature can be unpredictable and might generate unexpected results and bugs with each iteration. Automatic code generation helps to avoid the revision of millions of lines of code when changes are made to a display – even late in the project or during the testing phase – by providing a repeatable process with a

predictable outcome. For example, creating a simple blue box with a specific size using hand coding could be done in hundreds or even thousands of different ways. This increases the risk of error with the number of variations in code used across the project. To mitigate this risk, the automatic code generator will always generate the same code for the blue box in exactly the same manner, no matter how many times it is repeated.

Choosing to use tools with automatic code generation at the beginning of the project is crucial and will ultimately enhance productivity during the development process. With mandatory, safety-critical standards like DO-178B taking center stage in avionics certification, the ability to track and document HMI development is critical. The FAA requires that developers provide lengthy documentation tracking software development as part of the certification application process. This documentation can be manually created, but a code generator that is qualifiable to DO-178B comes

with many certification documents and test cases to show that the HMI has already undergone significant testing to the levels required by the FAA. When a customer leverages automatic code generators qualifiable to DO-178B, they can take credit for much of the testing and documentation that has already been accomplished and reduce the time and cost of certification.

#### Cut costs with standardization

New avionics systems, display functions, and widgets combined with the management of hardware obsolescence during the lifetime of a helicopter can cause project overhead to skyrocket. To manage these costs, developers can opt to follow ARINC 661. ARINC 661 allows developers to access a standard set of widgets, which are objects such as symbols, pictures, panels, and buttons. These are the basic building blocks of a Definition File (DF) that will be displayed in an HMI. The DF contains pages or "layers," made up of different widgets that will be displayed on the Cockpit

www.mil-1553.com

#### Partners in Thermal Management

DegreeC offers cooling solutions, airflow sensors and instrumentation, and testing services for Military applications backed by an 11 year track record of exceptional client service.

#### **Custom Cooling Solutions**

- Custom motor and fan controllers

- Fault tolerant electronics

- Highest performance heatsink solutions

- Rugeddized fan tray assemblies

#### Airflow Sensors, Switches, and Instrumentation

- · Airflow sensors for embedded applications

- Airflow switches for monitoring critical environments

- Multipoint airflow testing instruments

#### Thermal Design and Testing, Product Reliability, and **Predictability Analysis**

- Thermal Design and Airflow Testing

- MTBF Analysis

- EMI/C

- MIL-STD-1629. MIL-HBK-217F

- COTS Testing Programs

1-877-334-7332 www.degreec.com US, Japan, Mexico, China, & India

Display System (CDS). Using standardized widgets reduces the amount of time required to ramp-up on projects because it makes it very easy for a developer to understand how to develop new displays. Without a standard in place, developers have to rework the coding whenever a different combination of vendors is chosen to meet a variety of file format requirements. This standard set of preapproved building blocks gives a developer the flexibility to use systems from multiple vendors: The files follow a standard format and don't require data replication or additional coding. Finally, it is also possible to reuse large parts of a DF on a new project by modifying the visual appearance of widgets, eliminating the need to start from scratch every time.

Though it is not mandatory, industry leaders such as helicopter manufacturer AgustaWestland are benefiting from ARINC 661's guidelines. AgustaWestland selected the VAPS XT ARINC 661 module from Presagis because it allows the company to quickly develop concepts for the HMI and reduce risk by providing a future path for DO-178B certification.

Tools supporting ARINC 661 development can be used to develop the look and feel of a complete widget library without working on the actual hardware.

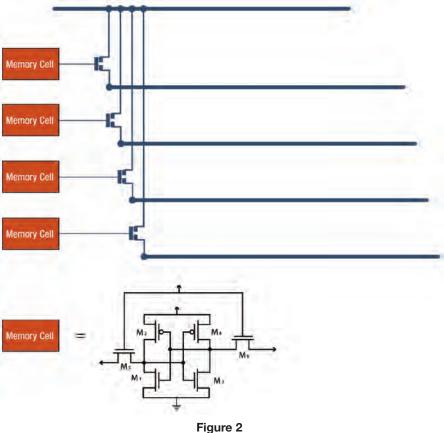

These widgets can be created graphically, using the low-level building blocks that are provided with the tools, or through programming. Objects created through programming need to be coded from scratch using traditional software coding tools, but when they are created graphically using a modeling tool, there is no coding involved. Developers use modeling tools to select aspects such as lines, colors, and text from the user interface, and the tool automatically generates the code for the completed object. This supports quick changes to their appearance during an iterative development process without needing to modify or create a single line of code. To define behavior of objects, developers will then use state-charts, such as the one depicted in Figure 2, to select elements of the design to create triggers and actions inside the application logic. By using ARINC 661-supported software, the need to repeatedly hand code behaviors across multiple widgets is eliminated. Instead the state-chart logic can be applied to each instance of a customer object, saving time and eliminating the risk of human error.

#### Put the HMI to the test in a simulated environment

Before the HMI is deployed to the cockpit, it is crucial to test its functionality. No

Figure 2

one wants to discover during pilot training that activating a combination of display functions in a specific sequence causes a critical system failure. No one wants to be forced back to the drawing board and have to repeat the entire development process either. Consequently, HMIs are evaluated on many criteria. For example, will the HMI allow pilots to act intuitively, helping them quickly make and execute the right decisions? In order to properly make this assessment, designers need to test the HMI in a simulated environment such as the one shown in Figure 3.

To ensure new HMIs will function as intended, they must be tested under a wide variety of conditions, such as brownouts, which occur when dust or sand in the air reduces in-flight visibility. By simulating a rich immersive environment, designers can test the HMI in a realistic 3D scenario that tests the ability of the HMI to process and present flight information. Creating a simulated environment for testing helps save money in the long run by allowing developers to see how the HMI functions before it is embedded into the cockpit. If anomalies such as alignment, usability, and performance issues are identified, an automatic code generator will become particularly handy, as it allows the developer to easily make changes and reiterate the process.

An advantage of using COTS tools for simulation and testing is that the software can be used across a multitude of platforms out-of-the-box. Avionics developers can take advantage of COTS tools to design HMIs and create the simulated environment for HMI testing. Using

Figure 3

# Rugged High-Speed Data Recording and Storage

Vortex Data Recording and Playback Systems

Fibre Channel Storage Area Network

Solid State or Rotating Media

#### Powerful

- Streaming data recording platforms with up to 720 MB/s per recording engine sustained recording performance

- Scalable Fibre Channel SAN architecture providing virtually limitless storage capacity

- · Ready-to-run application examples

#### **Flexible**

- Customer programmable or application specific recording and playback systems

- VXS (VITA 41), VME, CompactPCI and Industrial PC recording engines

- Solid state or rotating media options from rugged to commercial

#### Innovative

- Access and control using web browser or XML-RPC

- Disk grouping and intelligent disk management

Embedded Computing - Data Recording/Rugged Storage - Bus/Protocol Analyzers

For more information, please visit http://www.vmetro.com/recorder or call (281) 584-0728

Using simulation at the very beginning stages of development to test prototype concepts and receive early feedback from end users, avionics developers can eliminate the risk of creating an HMI that pilots do not find intuitive. "

simulation at the very beginning stages of development to test prototype concepts and receive early feedback from end users, avionics developers can eliminate the risk of creating an HMI that pilots do not find intuitive. By leveraging a simulated environment, they can also put the final HMI through its paces and test its maximum threshold. With COTS simulation software, developers can test the HMI while the pilot flies different missions in a simulated virtual environment.

#### The end result: A sophisticated, pilot-friendly HMI

The helicopter cockpit has evolved from an electronic flight instrumentation system to an integrated flight data system. As a result, HMI development projects have increased in complexity, presenting unique challenges and risks, such as coding errors, project overruns, and design flaws. To mitigate these risks, avionics developers can tap into useful features such as automatic code generation, support for industry standards, and simulation incorporated by COTS suppliers that have broad access to the marketplace. This allows avionics developers to leverage tools that have already been proven across a wide number of systems, which means they can minimize the amount of time spent developing tools and focus on what they do best: developing effective, pilotfriendly HMIs.

**Robert Kopersiewich** is vice president, product and program management, at Presagis, where he oversees and directs the growth and trajectory of the Presagis product portfolio and business road map. With more than 15 years of experience identifying and addressing key market needs, Robert plays a key role in the future success of Presagis. In 2004, he was named director of product management at Engenuity Technologies. Prior to joining Engenuity, he worked for a number of leading

companies in both the telecommunications and optical-disc industries. He can be contacted at Robert.Kopersiewich@presagis.com.

> Presagis 1-800-361-6424 www.presagis.com

Depicting material damage in military simulations has traditionally been a labor-intensive and expensive proposition. Now a new technology called Digital Molecular Matter (DMM), in conjunction with real-time Finite Element Analysis (FEA), promises to drastically improve simulation realism while reducing development time and cost.

Preparing war fighters for military engagement is both extremely important and extremely complex. The rules of engagement have changed over the years as battle lines are not always clearly defined. Today's war fighters are not trained simply to overtake the enemy. They must be aware of civilians caught in the proverbial crossfire of war. They must strive to achieve the goals defined for specific operations, minimizing any collateral damage that might come about.

Realistic training simulations depicting battlefield damage can help today's military achieve these goals, and that's where simulation designers and developers come in. They must seek out new technologies that enable the creation of more realistic simulations. They must also be agile in adapting simulations to the shifting requirements of the moment.

Demand for increasingly realistic simulations - combined with shortened development timelines - is creating tremendous challenges for military simulation designers, developers, and managers. A new technology called Digital Molecular Matter (DMM) uses real-time physical modeling to address these challenges, producing more realistic simulations

while meeting rapid design-to-delivery requirements.

#### The problem with art swapping

Recent advances in simulation platform technology allow for the rendering of highly realistic scenes; however, they do nothing to improve the kinetic realism that is just as important, if not more, than the visual realism – especially in military simulations. Stated another way, objects in the simulation need to look good, but they must also move and behave as realistically as they look.

Military simulations today rely heavily on art swaps or real-time substitutions of art assets to deform and break objects. When a projectile strikes a concrete wall, a script is run to show the wall crumbling. To create this effect in a simulation, artists have to draw hundreds of individual frames to show the slightest bit of motion or movement.

This approach limits an object's behaviors while greatly increasing the effort and time required to develop the simulation. A breaking pane of glass, for example, will always break the same way regardless of the simulated forces acting against it. Should a simulation require a change

of material, such as the addition of bulletresistant glass, new art assets need to be created and scripted to depict the new behavior. The time required to produce art swaps to depict kinetic effects drives up the cost of simulation development and can make the cost of updating an existing simulation prohibitive.

In an effort to improve kinetic fidelity, many simulations incorporate Rigid Body Dynamics (RBD) systems with art swapping to generate emergent behaviors. This approach has several disadvantages. Unconstrained emergent behaviors tend to produce unintended consequences and side effects, especially as the number of interactions between objects increases. And RBD is a very limited way of representing the physical properties of simulation objects. Simulation developers using RBD have only 10 variables to describe very complex materials: 3 translations, 3 rotations, mass, inertia, dampening, and coefficient of restitution (bounciness).

If simulation developers have any hope of meeting customer expectations going forward, they need a new approach that provides greater freedom to define and describe kinetic properties.

#### **FEA** provides thousands of degrees of freedom

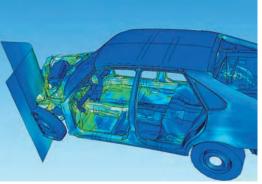

The most promising approach to kinetic fidelity is to utilize Finite Element Analysis (FEA) in real time. Using FEA, a solid object is divided into constituent subparts, or elements. Stresses applied to the object as a whole are interpreted as stresses to the individual elements. The result is a more granular and realistic view of how an object reacts to stress.

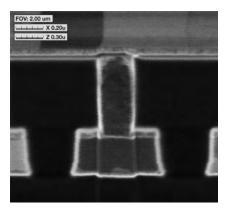

Offline FEA simulations have been used in the manufacturing industry for many years. FEA simulations are used to test and refine designs before the prototype phase of production - reducing the number of prototypes required, improving time-to-market, and reducing costs. Figure 1 shows how a car deforms using Finite Element Analysis.

FEA utilizes a mesh to discretize a solid object into a set of discrete elements. Calculations can then be applied to these elements to visualize where objects bend and twist and reveal the distribution of stresses and displacements. Utilized in a real-time simulation environment, FEA allows for a vastly more realistic representation of a simulated material. Armed with FEA in real time, simulation developers have thousands of degrees of freedom in describing how each discrete element can move and interact with the simulation environment. Moreover, the properties of these elements can be set to accurately behave like real-life materials: concrete crumbles; metal bends, deforms, and tears; and wood breaks and splinters. The result is kinetic fidelity never before seen in real-time simulations.

Materials can react in entirely new ways each time the user engages in the simulation. So when a tank drives through a brick wall at different angles, the wall will crumble differently each time. What is more, art objects developed with an FEA mesh are created once, and their fracture and deformation behavior is determined by their material properties and rendered in real time – eliminating the need for art swapping.

Not only is the software advancing, but processor technology has caught up. Modern processors can now run finite element-based simulations in real time.

Using real-time FEA technology, simulation developers can vastly improve the visual and kinetic fidelity of their simulations while reducing asset creation time and cost. Simulations no longer need be scripted scenarios, and time-to-deployment is exponentially faster.

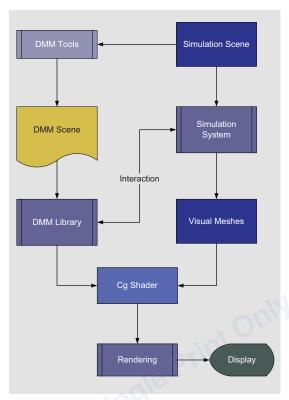

#### Digital Molecular Matter facilitates FEA

DMM is a real-time implementation of finite element physics. DMM technology is implemented as a real-time engine subsystem that runs independently of

Figure 1

the primary simulation system; it also includes the tools required to convert ordinary meshes created by artists into finite element volumetric meshes.

A key advantage of DMM is the ability to add FEA effects to new objects as they are created or to existing objects for enhanced capability. With minimal effort, simulation developers can leverage their existing investments by adding DMM capability to legacy simulations.

Originally conceived by Pixelux Entertainment for the gaming industry, DMM attracted the attention of LucasArts, who wanted to deliver state-of-the-art gameplay technology in its upcoming *Star Wars* and *Indiana Jones* video games while reducing production costs. In late 2005, Pixelux began working in partnership with LucasArts to develop and refine DMM into an artist-friendly technology that could deliver the promise of finite element physics.

Pixelux subsequently partnered with Objective Interface Systems (OIS) to adapt DMM to the military and aerospace simulation market. The resulting product, DMMfx, was introduced at the I/ITSEC 2007 trade conference.

DMMfx provides the means to deploy military simulations with realistic deformation and fracture of materials. Wood twists, splinters, and breaks like real wood; metal deforms, bends, and tears; and glass shatters like glass. Damage such as buckling, tearing, and fracture, along with collateral effects, occur in expected ways. Simulations perform with unpredictability and realism, making them more effective. Figure 2 shows a tank breaking through wooden fences in a simulation using DMMfx.

#### **DMM** architecture and implementation

The DMM subsystem runs independently of the primary simulation engine, exchanging information about forces

Figure 2

being applied to a scene, determining whether objects are being kinematically driven, as well as other physical interactions. Force feedback is a natural result of these interactions and can be used to generate additional visual effects and realistic sounds resulting from collisions and distortions.

The process for adding these effects is straightforward, utilizing techniques familiar to simulation artists. Artists start with a surface mesh for a new or existing object. This mesh is then used as the basis for a tetrahedral "cage." This cage is then used to create a tetrahedral mesh of the volume of the object. Finally, if the object

# What's on your Radar?

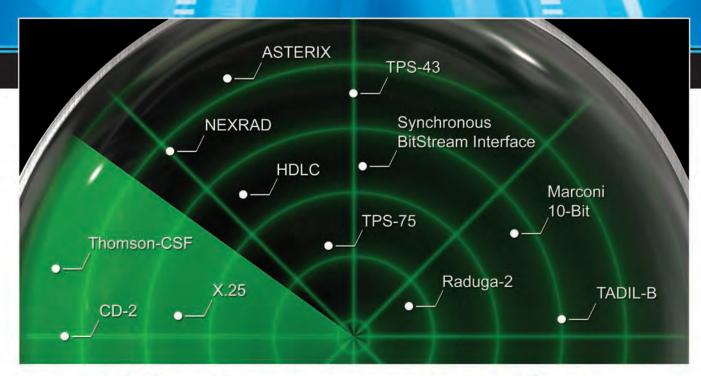

Performance Technologies' NexusWare® WAN protocol software provides a seamless connection to a broad range of telecommunications, aerospace and defense, and commercial applications for both emerging and legacy networks.

With over 25 years experience developing highly reliable and scalable solutions, we can provide you with integrated hardware and software that can meet your product needs today and allow for future migration tomorrow.

Managed WAN Gateways, Radar Extraction, Recording Servers, and Lawful Intercept Platforms are a few of the many applications that utilize our broad software offering. Available on a suite of hardware platforms in PCI™, PCI Express®, CompactPCI®, MicroTCA™, and stand-alone form factors, our flexible WAN protocol solutions can easily accommodate a wide range of data and communication network requirements.

Explore the limitless possibilities for your programs by calling Performance Technologies today.

Phone: 585.256.0200 • www.pt.com/radar5 • E-mail: info-request@pt.com

# The Flash Storage Leader

- . Ultra DMA Mode 6 Support

- . Compliant Compact Specifications

- . No Seek Error No Noise

- . Low Power Consumption

- . Shock Resistant & Anti-vibration

- No Latency Delay

- . RoHS

- . Form Factors in 1.8"/2.5"

- . SATA I, SATA II, IDE and ZIF Interface

- . SLC/MLC Flash IC Technology

**PQI** Corporation

Tel:(510)651-7281

Fax:(510)651-7240

For information, please contact:

dom@pqimemory.com

Learn more at: www.pgimemory.com

### Wide Temp.

-40 degree~+85 degree

On Sale

is breakable, the mesh has to be clipped against the surface mesh and have internal faces added that will be visible when the object breaks. Figure 3 shows a typical DMM workflow.

In addition, DMM also implements a visual enhancement called splinter geometry. Splinter geometry allows for the visually correct disintegration of objects that are naturally made up of component pieces such as wood, brick walls, and stone buildings. Splinter technology provides an increase in realism by fracturing objects in ways that appear more complex, without having to create a denser mesh. Figure 4 shows a timber being twisted and splintering.

DMM also provides the ability to optimize scene performance by compressing objects within a scene, or by freezing inactive portions of a scene to relieve the system from having to simulate unused elements. Meshes not in live use are made dormant until they are needed.

#### Better simulations, better results

Improving military simulations to realistically depict material damage is crucial to the success of today's war fighters. Going forward, military simulation developers cannot afford to con-

Figure 3

Figure 4

tinue to rely on art swaps to depict the fracture and deformation of objects, so a new approach is needed. Improvements in simulation platform technology make the implementation of real-time Finite Element Analysis through Digital Molecular Matter a practical solution. Using this approach, military simulation managers, designers, and developers can deploy more kinetically realistic simulations while reducing development time and cost. The result is a better-trained war fighter capable of meeting the demands of the battlefield today and tomorrow – while reducing collateral damage.

Steve Griffith is the director of business development for physical modeling and simulation at Objective Interface Systems. He has more than 20 years of business development, engineering, and management experience in the software industry. He can be contacted at steve.griffith@ois.com.

> **Objective Interface Systems** 703-295-6500 www.ois.com

#### Back on track:

#### JTRS JPEO assures open SCA and coalition use

#### **EDITOR'S NOTE**

Group editorial director Chris Ciufo and editor Terri Thorson conducted an exclusive interview with Dennis M. Bauman, Joint Program Executive Officer, Joint Tactical Radio System (JTRS) at the AFCEA West show in San Diego earlier this year. The key questions on their minds surrounded the progress of JTRS – which had just been essentially "rescued from the dead" after a "stop work" order had been rescinded – as well as how COTS and open architectures might benefit the many JTRS product lines. Edited excerpts follow.

MIL EMBEDDED: JTRS is all about interoperability between services, different waveforms, and hardware types. But how would you describe the applicability of the JTRS Software Communications Architecture (SCA) to all of your vendors - and to the greater SDR industry at large?

BAUMAN: We think it's very open, based on our SCA and APIs. There are 26 of them currently [corresponding to the JTRS waveforms]. Those are the Increment One APIs, and we're continuing to refine them for future increments. What we do is obtain government-purpose rights on all the software developed on JTRS, and then we put it into an information repository. The repository is like a library, and we give out library cards to any industry people who want it. But they have to agree to, number one, use it for government purposes and tell us what they are using it for. Number two, if they change it, they've got to give back the changed code for the repository with government-purpose rights or better.

So JTRS is not quite as open as Linux because we have security issues that Linux doesn't, but we think we are pretty close. What we achieve by doing this is reusability and the resulting cost savings, along with interoperability because we are using the same software across all our products. This allows us to swap out vendors because we have these kinds of "Lego" building blocks in our repository. So if we aren't getting what we want from one vendor, we can buy that same module from another vendor.

MIL EMBEDDED: To what extent have you verified that Boeing's SCA implementation, for example, is consistent with GE Fanuc's SCA implementation?

One detractor to it, though, is that we make [JTRS] so open that a lot of vendors who embed their own Intellectual Property and are dependent upon maintaining IP are a bit taken aback by how open the standard can be.

BAUMAN: We have something called the JTEL lab, which tests and certifies all products for SCA compliance. The lab does that through a series of automated tools that go through and look for possible discrepancies that are then flagged. Next, the lab performs manual tests and inspections to determine whether a vendor's product meets the SCA. If it doesn't, then we send specific problems back to the vendor and get them to correct them.

MIL EMBEDDED: So could you, API issues notwithstanding, unbolt Thales' implementation of SCA and marry it to a Boeing AMR cluster?

BAUMAN: We're doing that already. The waveforms that are going to be used in Boeing's products are produced by a variety of vendors, for instance, ITT is under contract to do SRWs. There are multiple vendors who are under contract and are producing waveforms that are going to go on all the different boxes. That's the whole idea of the repository, and the whole operating environment on GMR was shared and used on MIDS-J [Multifunctional Information Distribution System].

MIL EMBEDDED: How many of the original 32 waveforms are still being ported and made SCA compliant?

BAUMAN: I'd have to check the number. but it's between 9 and 12. But we didn't drop the others. One of the things we did in the short term was go for a "big bang" approach to JTRS, with the incremental approach. And so in Increment One, we have a subset of those original 32 waveforms, decreased down to the 9 or 12, but we also added a couple.

Anyway, everybody says we shrunk the requirement, but that's not entirely true. We shrunk it in some aspects, but we went from a single waveform networking form, WNW, to three of them in Increment One, for example. The reason is that there's a difference in number, like in UHF satcom. If you count 181, 182, 183,

and 184 as four different waveforms, then you have a different number at the end than if you count UHF satcom as one waveform.

MIL EMBEDDED: To what extent do you think the SCA will be adopted by the commercial market, which was one of the original pushes of the program?

BAUMAN: I don't know. I know that it's being seriously considered for adoption by our international coalition partners. There was at one point a push in Europe to build their own SCA, and that's atrophied. You know that you could define many standards that are like the SCA (yet different), and they'd probably work just as well. But what we're trying to convince the world is, here's one that's here, so why not use it?

MIL EMBEDDED: Are there any definite outreach efforts to the likes of Nokia, Ericsson, or other civilian companies?

BAUMAN: We have done that through the Software-Defined Radio Forum. Quite frankly, we're seeing a lot more traction with that in the past six months. And the reason for it is that if you compare where JTRS is now with the big downturn in the IT world, there was a big "Let's go from second-generation cellular to third-gen" push five years ago. Well, the business case in light of the downturn just wasn't there. But now you're seeing some of the third- and fourth-generation cellular products being rolled out. So there is now increased interest on the industry's part to look for more open systems standards, and we have one that's perfectly viable. One detractor to it, though, is that we make it so open that a lot of vendors who embed their own Intellectual Property and are dependent upon maintaining IP are a bit taken aback by how open the standard can be.

MIL EMBEDDED: To what extent do you think any JTRS implementation is going to utilize cognitive radio capabilities?

BAUMAN: We consider cognitive radio to be at the forefront of technology. Well, one thing you do as an acquisition fundamental is you don't adopt technology before its time. I think cognitive radio technology is very promising: It can help us with spectrum - and in a lot of ways. But it's too leading edge to put into

production at this time. We are working with DARPA on that. Actually, I believe cognitive radio is a capability cap in Implement Two that we're currently looking at. But it's not ready for prime time, and we're not putting it into Increment One as part of our requirements discipline.

MIL EMBEDDED: What are your plans for tech refresh?

BAUMAN: Our plans for tech refresh will be part of Increment Two, and we will be filling capability gaps as defined by the JROC [Joint Requirements Oversight Council] as part of the requirements process. When we roll out the new capability, we intend to do technology refresh as needed in that same development to minimize future changes to our boxes' architecture and thereby preserve affordability. When you make a fundamental architecture change, there's a very long process with the NSA to make sure you don't have a vulnerability. We want to be careful that we don't require ourselves to spend more money recertifying and restudying that architecture. So we'll be doing technology refresh in terms of upgrading processors, and upgrading all

sorts of technology. But we would like to maintain stability in the fundamental architecture for some time.

MIL EMBEDDED: To what extent are there requirements on the table or being talked about for coalition interoperability or Non-Governmental Organization (NGO) interoperability?

BAUMAN: First of all, our MIDS program is a cooperative program paid for by five nations: the U.S., France, Italy, Spain, and Germany. MIDS-LVT was that way, and MIDS-J has financial participation from our allies. Our plan is to deliver a tech data package to them at the end of the MIDS-J core radio development, which is coming up soon. We are also working with those particular countries in terms of them developing their own capability, based on our design (or buying our capability).

We also have the U.K.'s Bowman waveform – through formal qualification tests and in our repository. And as part of our enterprise business model, we are making that waveform available to all vendors so that they can add it to the radios they're already selling. We're hoping that Thales and Harris might port the Bowman waveform to their JEM and Falcon III products that we're already buying, which would allow us to buy that capability from existing contracts. We also have a coalition waveform development effort with primarily European allies, and that's just getting underway. Beyond that, we're also looking at a coalition wideband networking waveform tool to allow networking interoperability among the U.S. and coalition partners.

We have some difficulty with taking our waveforms and giving them to everybody in the world. We have an information repository within the U.S., for U.S. vendors, for U.S. government purposes. For security reasons, it's not quite easy to give that code away to our allies. It's not something that we will probably do directly. But that doesn't preclude us from working on a waveform with our coalition partners, and that's exactly what we're doing.

Dennis M. Bauman has been a Joint Program Executive Officer, Joint Tactical Radio System, since 2005. His current job duties include directing all waveform, radio, and common ancillary equipment development; performance and design specifications; standards for system operation; and JTRS systems engineering. Previous positions include Weapons Officer and Qualified Surface Warfare Officer in the U.S. Navy, Software Manager for the Naval Ocean Systems Center in San Diego, Head of the Operational Systems Branch of the Submarine Communications Division, and SPAWAR Program Director for C2I and Combat Support Applications, among others. He earned his Bachelor's degree from Pennsylvania State University and a Master's degree in Computer Science from the University of California at San Diego. For more information on JTRS, email jpeo\_jtrs\_help\_desk@navy.mil.

> JPEO JTRS http://jpeojtrs.mil

#### **MODULAR SOLUTIONS** FOR MIL-STD-1553

#### PMC-1553 Dual SUMMIT

Dual UTMC 1553 SUMMIT Controller Bus Controller, Remote Terminal, Bus Monitor modes

- 1 or 2 UTMC SUMMIT

- UT69151DX-GPC

- BC / RT / BM

- On-chip Transceivers

#### **CPCI-1553 SUMMIT**

Single or Dual UTMC 1553 SUMMIT Controller Bus Controller, Remote Terminal, **Bus Monitor modes**

- UTMC SUMMIT

- UT69151DX-GPC

- 128Kbytes SRAM

- On-chip Transceivers

#### PMC-1553 DDC

Single or Dual DDC ACE 1553 Controller Bus Controller, Remote Terminal, Bus Monitor modes

- DDC ACE BU61580S3

- 128Kbytes SRAM

- On-chip Transceivers

#### **MAXIMIZE YOUR SPACE CUSTOMIZE YOUR 1553**

Whether for PCI, CPCI, IP or PMC, ALPHI provides the MIL-STD-1553 solution that you need for your Mission Critical Systems.

From 1 to 4 channels, Aeroflex SUMMIT, or DDC ACE, MiniACE and Micro ACE.

ALPHI also offers an intelligent choice of IndustryPack Carriers allowing you to create your own dedicated MIL-STD-1553 solution.

Contact us at: 480-838-2428 or visit our Web site at www.alphitech.com

TECHNOLOGY CORPORATION

# When You're at 30,000 feet Quality Matters

Our Products and Services are Second to None

t VersaLogic we know about building dependable, high reliability embedded computers for mission critical applications. Our products have been designed into some of the most sophisticated and high profile military and aerospace equipment used today. Every board we make is run through exhaustive inspections and quality tests, ensuring that we deliver only the best. And with our world class service and five year availability guarantee, we'll always be there when you need us. Whether you need one of our standard products or a customized version, our skilled technical staff will work with you to meet your exact requirements. So before your program launches, choose the company with the quality and service to take you where you need to go.

Contact us to find out how for more than 30 years we've been perfecting the fine art of extra-ordinary support and on-time delivery: One customer at a time.

flexibility and system-level savings. But are FPGAs always better than their ASIC rivals?

Digital-Down Converters (DDCs) have become a cornerstone technology in communication systems. Similar to its analog receiver counterpart, the DDC provides the user with a means to tune and extract a frequency of interest from a broad radio spectrum. Over the past few years, the functions associated with DDCs have seen a shift from being delivered in ASICs to operating as Intellectual Property (IP) in FPGAs.

For many applications this implementation shift brings advantages including: design flexibility, higher precision processing, higher channel density, lower power, and lower cost per channel. During the past three to four years, with the advent of each new higher performance FPGA family, these benefits continue to increase. Bob and Rich, through practical examples, explore some of these key benefits of implementing DDC designs in FPGAs - including more flexible designs and system-level savings on board count, space, and power. But are ASICs ever a better choice than FPGAs?

#### **Digital-Down Converter** fundamentals

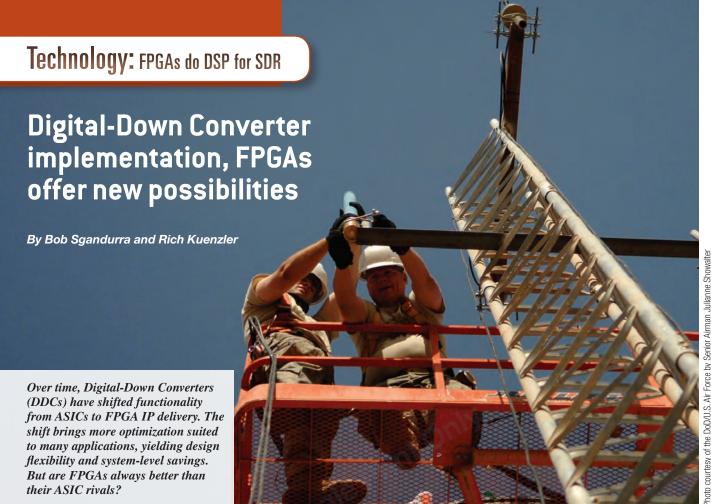

To understand how FPGAs play a key role in implementing DDCs and performing the function of a receiver, it's important to break the DDC down into its individual functional blocks. Figure 1 shows a classic DDC. Regardless of whether it's implemented in an ASIC or an FPGA, this is a common architecture used to perform the DDC function.

The first stage of the DDC uses a digital mixer to frequency translate a specific channel frequency down to baseband using a pair of multipliers and a Direct Digital Synthesizer (DDS). This function enables the user to tune the receiver to the desired frequency of interest. The second stage of the DDC reduces the sample rate of the signal to match the desired channel output bandwidth using a Cascaded Integrator Comb (CIC) filter to decimate

the data. A second CIC filter provides a coarse gain adjustment stage. The signal is then passed to a pair of additional polyphase filters: First, a Compensation Finite Impulse Response (CFIR) filter, then to a Programmable Finite Impulse Response (PFIR) filter. This filter pair provides additional decimation and final signal shaping prior to the rounding stage and final output.

When you get past all the acronyms and realize that most of the individual function blocks of the DDC are implemented using multipliers, it starts to become apparent how the DDC might map into current FPGA families. Most newer FPGAs include a wealth of DSP function blocks that are primarily multipliers.

Figure 1

| DDC implementation   | Number of channels | Decimation range | Input rate<br>(MSps) | SFDR | Tuning resolution | Area per<br>channel (mm²) | Power per<br>channel (W) | Cost per<br>channel (US\$) |

|----------------------|--------------------|------------------|----------------------|------|-------------------|---------------------------|--------------------------|----------------------------|

| Xilinx DDC V1.0 core | 19                 | 4-1048512        | 110                  | 108  | Integer steps     | 64.5                      | .63                      | 78                         |

| Pentek 430 DDC core  | 256                | 1024-9984        | 110                  | 110  | Steps of 256      | 4.7                       | .01                      | 3                          |

| Pentek 420 DDC core  | 2                  | 2-64             | 110                  | 118  | Binary steps      | 612.5                     | 2.5                      | 420                        |

| GC5016               | 4                  | 1-4096           | 160                  | 115  | Integer steps     | 72.3                      | .25                      | 41                         |

Table 1

Additionally, the general-purpose logic resource and on-chip memory of FPGAs also match the requirements of the DDC for implementing the required FIR filters and filter coefficient tables.

#### Design flexibility: DDCs as intellectual property cores

As part of their intellectual property library series of IP, Xilinx provides a free DDC core. This Digital-Down Converter core is the basic building block of multichannel DDCs. It follows the classic DDC architecture (Figure 1) and provides a total decimation range of 4 to 1048512. As a generic building clock, it needs to satisfy a wide range of applications and can't really be optimized for a specific range. In addition to the Xilinx core, IP is available from a number of companies providing more options and better optimization to match specific applications. Two of these cores are offered by Pentek, implemented in a Virtex-II Pro 50. The 430 DDC core is optimized for high channel count/narrow bandwidths, while the 420 core is optimized for wider bandwidths and better Spurious Free Dynamic Range (SFDR) but with fewer channels. Table 1 compares these choices with a popular ASIC-based DDC solution from Texas Instruments.

When compared on a size/power/cost per channel basis, it becomes apparent that narrowband, high channel count DDC cores can be very efficiently implemented in FPGAs. Implementation of wideband DDCs tends to consume many more FPGA DSP and logic resources, limiting the number of channels that can fit in a single FPGA, thus reducing the overall savings. But even with less cost-effective wideband DDCs, the custom IP approach can sometimes provide the only viable solution when a specific performance characteristic is required like extended SFDR, for example.

#### IP enables flexibility in software radio products

Aside from stand-alone IP cores available from Xilinx and other IP vendors, some vendors are offering FPGA-based integrated communications receiver products that offer the IP preinstalled. As stated earlier, custom IP or cores can be optimized to address a specific application, enabling more efficient use of FPGA resources and yielding better performance.

The flexibility this optimized core approach delivers becomes more apparent when products are provided by the same vendor and are actually the same hardware with only changes to the IP core. A system engineer can design a single

#### Tailored to your exact specifications

Whether you need one cabinet enclosure or one thousand, Optima EPS' custom design services will fit you like a glove. Based on proven platforms, Optima's modular design allows customization to be faster, easier, and less costly. With proven strength-to-weight ratios, and MIL-tested rugged designs, Optima can provide the Seismic, MIL-COTS, or Harsh Environment model cabinet you require. Call Optima today - we've got your needs covered from head to toe.

Phone: 770-496-4000 Web: www.optimaeps.com Email: sales@optimaeps.com

**MIL Rugged Cabinets**

Designed to MIL-STD: 461D, 810F, 167, 901D

Seismic Cabinets

- Meets Seismic Zone 4 per GR-63-CORE

- Tested to MIL-STD-810F

Deployed Transportation

- EMC and NEMA-rated versions available

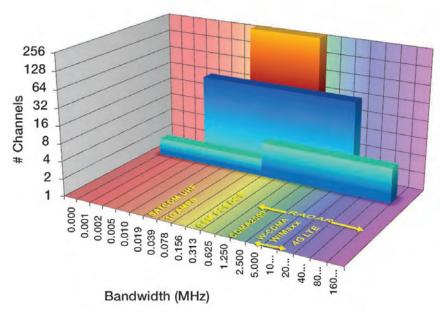

hardware receiver product and use it across a range of different application spaces. Additionally, some single applications, like Joint Tactical Radio System (JTRS), need to operate across a wide spectrum to handle diverse signal types. Figure 2 shows three optimized cores versus a non-optimized core across a range of applications, and the number of channels and bandwidths they typically require. Again this wide range of applications can be satisfied by using the same hardware, but different, optimized IP cores. This is one of the fundamental concepts of Software-Defined Radio (SDR), and is difficult or sometimes impossible to achieve with ASIC-based solutions.

#### **System-level savings**

So let's take a look at a complete receiver system. One common application is GSM 2G, a high channel count, lowbandwidth system. An E-GSM receiver requires 174 channels spaced 200 KHz apart. Just three or four years ago, a viable solution would have used TI/Graychip four-channel 4016 ASIC-based DDCs.

Figure 2

A common board form factor for these types of applications is PMC, a compact I/O module for VMEbus systems. One PMC can house two 100 MHz A/Ds and four 4016s and all of the required

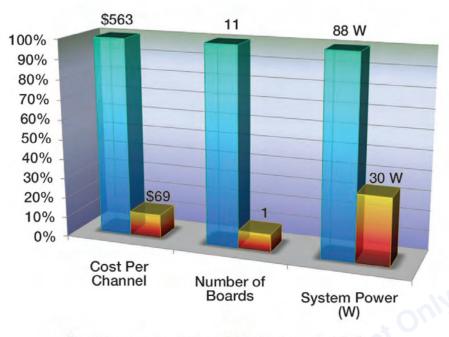

interface and support circuitry. For a 174-channel system, this would require 11 PMC modules. By comparison, an IP DDC with 174 channels and similar performance to the 4016 can fit in a single Virtex-5 XC5VSX95T FPGA that can be housed on a single PMC, along with two channels of 200 MHz A/Ds and all support circuitry. The PMC board count, along with cost, space, and power, can be greatly reduced as shown in Figure 3.

#### **FPGAs versus ASICs**

FPGAs continue to offer new possibilities and performance when addressing processing tasks like Digital-Down Conversion. With each new generation of higher-performance FPGAs, processing precision continues to increase, enabling IP-based DDCs to outperform their ASIC-based cousins with specifications like better Spurious Free Dynamic Range.

From a system-level view, it's easy to understand how packing many channels of DDCs into one or two FPGAs can reduce the board count, power requirements, and cost over a solution that requires 30 or 40 individual ASIC DDC chips to run the same application. Additionally, FPGA solutions can be extremely flexible by supporting vastly different signals with the simple load of an IP core and reusing the same hardware platform.

However, FPGAs are not a perfect match for all requirements. They show the greatest advantages in systems with

#### E-GSM 174-Channel Receiver Application

ASIC-based solution FPGA-based solution

Figure 3

high channel densities and typically narrower bandwidths where many DDC channels can fit on a single FPGA. In systems with just one or two channels and very wide bandwidths in the range of 100 MHz or greater, the higher cost of the FPGAs needed to fit the larger wideband DDC cores can quickly exceed the cost of designing the system with a single multi-channel DDC ASIC.

So, while cost, size, and power are important factors in designing a receiver system, ultimately the technical requirements may dictate the choice of whether an ASIC or FPGA is used.

Richard Kuenzler is a senior design engineer at Pentek, specializing in the development of DSP, I/O, and software radio hardware products. During his 17 years in the DSP industry, Rich also worked for Hughes and Raytheon where he specialized in image processing and the development of military night vision systems. He holds a Bachelor's degree from Syracuse University and has been published in various electronic industry magazines. He can be contacted at Kuenzler@pentek.com.

Robert Sgandurra serves as senior product manager over Pentek's DSP, data acquisition, digital receiver, and software products. He joined Pentek in 1994, working as an application engineer and system integrator, taking on the responsibility of product manager in 1997. Prior to Pentek, he worked seven years in the medical electronics industry designing and managing projects for ultrasound imaging. He holds a BSCS from the New York Institute of Technology. He can be

contacted at Bob@pentek.com.

Pentek, Inc. 201-818-5900 www.pentek.com

Today's high-density FPGAs offer designers an opportunity to quickly create customized components for optimum performance and rapid deployment of mission-critical systems. But for military and aerospace applications, memorybased FPGA technology is known to fall short in addressing several important requirements, including radiation resistance and design security. Anti-fuse FPGA technology successfully addresses these requirements to bring the advantages of programmable logic to mission-critical system design.

Many developers understand that missioncritical systems must be designed for reliable operation in extreme environmental conditions, but find that most FPGA technologies are hard-pressed to meet these needs. Further, there are other requirements that can be just as critical in determining a device's suitability for mission-critical service where most FPGA technologies fall short. Our discussion will focus on three of these other key requirements: nonvolatile configuration, reliable operation in a radiation environment, and design security (Table 1).

#### Trio of factors affect critical apps